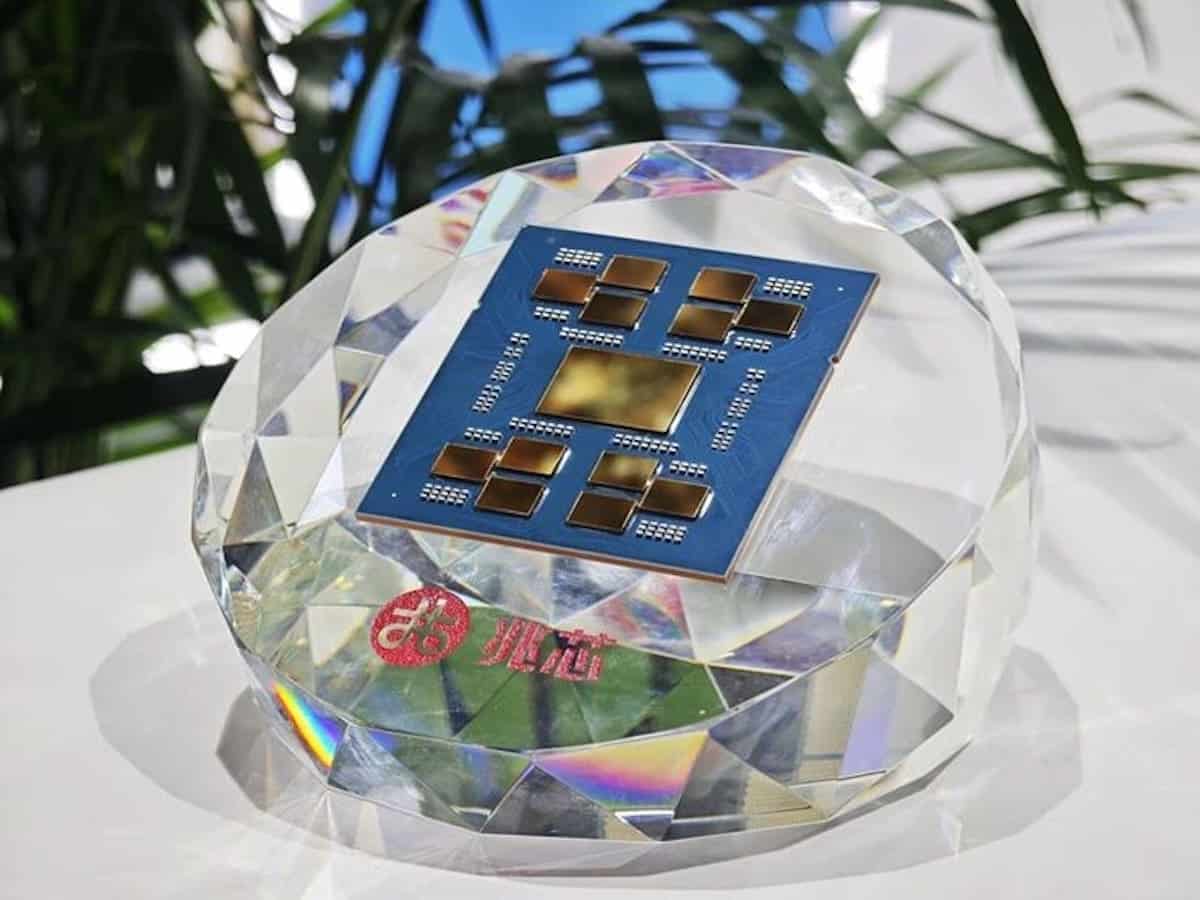

A few days before the 76th anniversary of the founding of the People’s Republic of China, Zhaoxin has published an extended technical sheet on its official website for the new family of KaiSheng KH-50000 servers. The company presents the launch as a “technological offering,” and beyond the symbolism, provides a detailed specifications sheet that notably boosts compute density, modernizes the memory and I/O subsystem, and strengthens both security and the domestic x86 ecosystem.

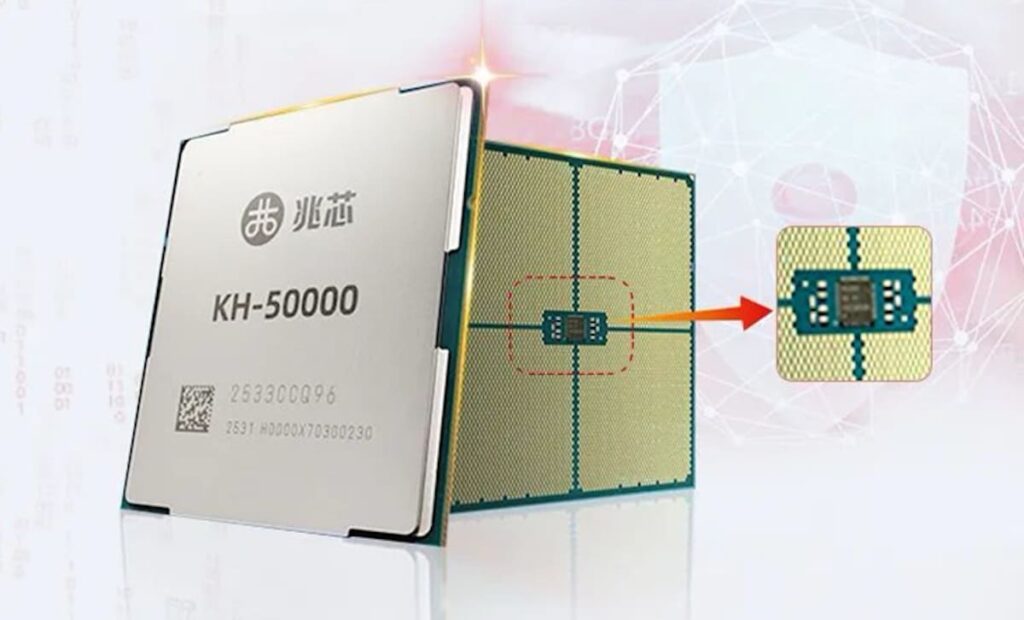

The KH-50000 series adopts Chiplet packaging and, in its top configuration, integrates 12 CPU dies per socket to reach 96 cores (with a variant of 72 cores). The leap over the previous KH-40000 generation — which in single-processor configuration reached 32 cores — is significant: it triples the number of cores per socket and opens the door to quad-socket machines with up to 384 general-purpose cores inside a single chassis.

Below are the five key technical highlights that define this offering.

1) Chiplets and cores: 12 dies per socket, 96C/72C, and up to 384 MB of L3

Zhaoxin confirms two initial SKUs:

- KH-50000 (96C) — 96 cores, base frequency 2.2 GHz, boost up to 3.0 GHz.

- KH-50000 (72C) — 72 cores, base frequency 2.6 GHz, boost up to 3.0 GHz.

Both variants share a maximum L3 cache of 384 MB, indicating a design with large-scale shared L3 to reduce contention in highly parallel scenarios (databases, analytics, microservices). The adoption of Chiplet allows Zhaoxin to separate compute, I/O, and potentially, memory into reusable blocks, facilitating manufacturing yields and product scalability without fully redesigning each die.

Industry insight: Moving from 32 to 96 cores per socket in a single generation places Zhaoxin among high-density x86 servers, a requirement to consolidate cloud workloads, AI inference, and edge services in few U, with a direct impact on TCO (more cores per rack, less peripheral hardware per VM/container).

2) Memory and I/O of today: 12× DDR5-5200 ECC (up to 3 TB) and large-scale PCIe 5.0

The KH-50000 platform raises the bar for bandwidth and capacity:

- Memory: 12 channels DDR5-5200 ECC, with up to 3 TB per socket. This increased bandwidth is key to support 72-96 cores in memory-bound workloads and to host larger AI models for inference near the data.

- PCle: 128 PCIe 5.0 lanes (with CXL support and the ZPI link), plus 16 PCIe 4.0 lanes, 4× USB 3.2 Gen2, and 12× SATA 3.2. The double PCIe generation provides flexibility for GPUs, NICs 100/200/400G, NVMe controllers, and various accelerators, while CXL enables coherency and expanded memory with next-generation devices.

- Proprietary interconnects: Mention of ZPI (Zhaoxin Processor Interconnect) and especially ZPI 5.0 places the interconnection fabric at the core of the design (see next section).

Industry insight: DDR5-5200 at 12 channels and PCIe 5.0 across 128 lanes are current credentials in server markets. The nod to CXL signals ambition for an open ecosystem supporting shared memory and pooling.

3) Multi-socket scaling and ZPI 5.0: up to 4 ways and 384 cores with lower latency and power consumption

Zhaoxin promises configurations of 2 and up to 4 processors per server. With KH-50000 of 96 cores, a quad-socket machine would total 384 x86 cores. The new ZPI 5.0 —the in-house interconnect— is the pillar expected to support this increased scale with wider bandwidth, lower latency, and improved energy efficiency.

- Official goal: enable general-purpose HPC/analytics platforms and dense AI servers (for inferences and pre/post processing), where inter-socket latency and coherency matter, especially if the links aren’t optimized.

- Practical effect: expand the application scope from traditional cloud services to big data engines leveraging NUMA consciously and supporting mixed CPU-accelerator workflows.

4) Security and reliability: SM2/SM3/SM4, TPM 2.0, GM/T 0012-2020, and reinforced RAS

Zhaoxin emphasizes a security block aimed at critical sectors:

- National cryptographic acceleration: supports SM2, SM3, and SM4 (a family of Chinese commercial cryptography algorithms) via accelerated instructions.

- Secure boot and key management, with improvements in RAS (reliability, availability, serviceability) at the server level.

- Trusted computing: integration of Guomin Technology’s 4th generation trusted computing, featuring the innovation “安算合封” (co-packaged security functions), compliant with GM/T 0012-2020 (cryptographic modules) and TPM 2.0 (SPEC 1.59).

Industry insight: this security block is crucial for public administration, finance, telecommunications, and healthcare, where compliance and sovereignty carry weight comparable to performance. Zhaoxin aims for a security pillar that is hardware-first, reducing reliance on peripherals or additional modules.

5) A “proprietary” x86 ecosystem, without sacrificing compatibility: SSE4.2, AVX, AVX2, virtualization, and domestic Linux distributions

To gain traction, Zhaoxin emphasizes x86 continuity:

- Instruction set: SSE4.2, AVX, and AVX2.

- Virtualization: supports CPU and I/O virtualization (foundation for cloud and multi-tenant setups).

- Operating systems: compatible with Kylin (银河麒麟), UnionTech/统信, and Zhongke Fangde/中科方德, forming the core enterprise Linux ecosystem domestically.

Industry insight: maintaining x86 compatibility reduces friction with legacy applications and middleware, while enabling Zhaoxin to build a local ecosystem (compilers, libraries, drivers) without starting from scratch.

Which servers does the KH-50000 enable (and where do they fit)

Zhaoxin envisions it as a base platform for assembling:

- High-performance general servers (IaaS, PaaS, transactional and analytical databases).

- High-density AI servers (inference and pre/post-processing near data, with accelerators via PCIe 5.0/CXL).

- High-density storage servers (numerous PCIe/SATA lanes and ample memory).

- High-performance workstations (simulation, compilation, CPU rendering).

- Cloud/edge platforms (12 DDR5 channels, modern I/O, and connectivity suitable for NICs and accelerators in dense 1U/2U formats).

The promise is to provide a “self-sufficient compute backbone” for AI, cloud, data centers, and mass storage, capable of supporting digital transformation from office to critical operations.

Strategic context and insights

- Density and modernity. Moving to 96C/72C per socket, DDR5-5200 in 12 channels, and PCIe 5.0 with 128 lanes positions Zhaoxin among current-generation server hardware.

- NUMA scaling (up to 4 ways). With ZPI 5.0, Zhaoxin aims to compete in large configurations — deep NUMA — still relevant in HPC and databases.

- Sovereign security. Compliance with national standards (SM2/3/4, GM/T 0012-2020) and TPM 2.0 targets regulated sectors prioritizing technological sovereignty.

- x86 and ecosystem. Reinforcing x86 — with AVX/AVX2 and local Linux — facilitates adoption by companies with little or no software porting effort.

What the official communication does not specify — and should be evaluated once silicon and boards are available — is the microarchitecture (IPC, scheduler, cache hierarchy per die, L3 topology), the sustained frequency under known TDP scenarios, and the performance per watt relative to international alternatives. Latency and bandwidth of ZPI 5.0 and its scaling under NUMA-heavy loads will also be critical.

A piece of the “cloud-edge-device” puzzle

Zhaoxin frames the KH-50000 as the spine of its proprietary compute ecosystem — “cloud-edge-device” (云-边-端). The family will align with KaiXian KX-7000 and other products to form a portfolio covering from data centers to personal terminals. The declared goal: to sustain — with domestic technology — the information security and the high quality of the digital economy.

Summary sheet for KaiSheng KH-50000

- Process and packaging: Chiplet with 12 CPU dies per socket.

- Cores and frequencies: 96C @ 2.2 GHz base / 3.0 GHz max, 72C @ 2.6 GHz base / 3.0 GHz max.

- Cache: L3 up to 384 MB.

- Memory: 12× DDR5-5200 ECC, up to 3 TB per processor.

- I/O: 128× PCIe 5.0 (with CXL and ZPI), 16× PCIe 4.0, 4× USB 3.2 Gen2, 12× SATA 3.2.

- Multi-socket: 2/4 ways with ZPI 5.0; up to 384 cores per server.

- Security: SM2/SM3/SM4, secure boot, key management, improved RAS, TPM 2.0 (SPEC 1.59), GM/T 0012-2020.

- Instructions and virtualization: x86, SSE4.2, AVX, AVX2; supports CPU and I/O virtualization.

- Operating systems: Kylin, UnionTech/统信, Zhongke Fangde/中科方德.

Conclusion

With the KH-50000, Zhaoxin marks a generational leap that places it among current x86 servers: more cores, cutting-edge memory and I/O, ambitious multi-socket configuration, and a security pillar aligned with both domestic and international standards (TPM). The actual performance —IPC, performance per watt, NUMA analysis— remains to be seen, but on paper, the platform opens doors to cloud and edge deployments with own silicon, and critical verticals demanding sovereignty without sacrificing x86.

If the ecosystem —compilers, libraries, drivers, hypervisors, and distros— develops properly, the KH-50000 could become a pillar of local cloud/AI infrastructure. And as a reminder: the race for general compute isn’t just about GPU; the CPU powering orchestration, storage, and security remains pivotal.

Frequently Asked Questions

How many cores does the Zhaoxin KaiSheng KH-50000 have, and at what frequencies does it operate?

The KH-50000 series comes in two versions: 96 cores (2.2 GHz base, up to 3.0 GHz) and 72 cores (2.6 GHz base, up to 3.0 GHz). Both share up to 384 MB of L3 cache and employ Chiplet packaging with 12 CPU dies per processor.

Does the KH-50000 support DDR5-5200 and PCIe 5.0? What is its memory capacity?

Yes. It features 12 DDR5-5200 ECC channels with up to 3 TB per socket. For I/O, it provides 128 PCIe 5.0 lines (with CXL and ZPI), along with 16 PCIe 4.0 lines, 4× USB 3.2 Gen2, and 12× SATA 3.2.

What security technologies does it include (SM2/SM3/SM4, TPM 2.0), and what are their purposes?

The KH-50000 accelerates cryptography with SM2/SM3/SM4, supports Secure Boot and key management, and enhances RAS functionalities. It incorporates the 4th generation of national trusted computing, complies with GM/T 0012-2020, and supports TPM 2.0 (SPEC 1.59) for increased reliability and security in critical sectors.

Is x86 compatibility maintained, and which operating systems are supported?

Yes. It supports x86 with SSE4.2, AVX, and AVX2, along with CPU and I/O virtualization. Compatible operating systems include Kylin, UnionTech/统信, and Zhongke Fangde/中科方德, forming the core of domestically developed enterprise Linux ecosystems.

How many sockets can a server with the KH-50000 scale to?

Zhaoxin envisions configurations of 2 and up to 4 processors per server, interconnected via ZPI 5.0. With 96 cores per socket, a four-way setup would total 384 x86 cores within a single server.