SK hynix continues to consolidate its leadership in the server DRAM sector with the development of an innovative validation process that ensures compatibility and performance of its latest DDR5 memory at 1c. This technology, the first of its kind to use the 1c node, represents a milestone in speed efficiency and energy consumption while adapting to the demands of an increasingly diverse server CPU market.

The latest installment of SK hynix’s series “Rulebreakers’ Revolutions” highlights the crucial role of validation in advancing DDR5, a process that has been essential for maintaining the reliability and performance of this next-generation memory. In this context, SK hynix has implemented differentiated strategies that allow it to face the challenges of a market where, in addition to Intel, AMD and Arm-based suppliers are gaining ground in cloud computing and specialized workload segments.

Adapting to a Diverse CPU Market

Traditionally, the server CPU sector has been dominated by Intel, allowing semiconductor companies to focus their validation efforts on a single architecture. However, the growing presence of AMD and Arm-based suppliers has fragmented the market, requiring SK hynix to adapt its DDR5 to ensure compatibility with multiple architectures. This includes early collaboration with customers during the product planning phase to ensure that DDR5 meets the standards and requirements of various CPU suppliers.

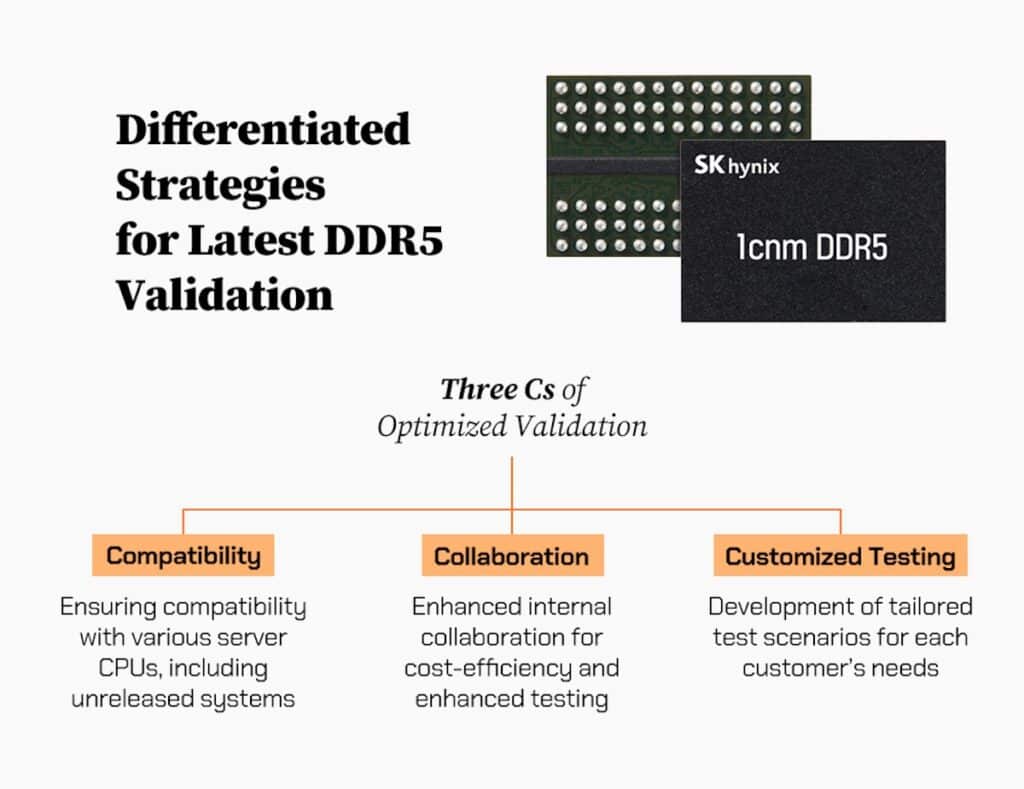

Innovation in Validation: Compatibility, Collaboration, and Customized Testing

To ensure the compatibility of its 1c DDR5 across various platforms, SK hynix has expanded its validation process. This approach, known as “the three Cs” (compatibility, collaboration, and customized testing), focuses on verifying that designs meet JEDEC standards, as well as creating specific tests for each customer based on real-world usage scenarios.

The validation process begins in the pre-development stage and is conducted in collaboration with SoCAn SoC, short for Security Operations Center… (System on Chip) companies, who validate the product in real applications. These tests are also supplemented by rigorous internal testing that identifies and resolves defects before sending samples to SoC partners. This combination of testing ensures that DDR5 memory modules maintain optimal performance under real-world conditions and across different CPU configurations.

Validation as a Driving Force in DDR5 Technology

Since the launch of the first DDR5 in 2020, SK hynix has utilized a robust validation strategy that has facilitated milestones such as the validation of its 1anm DDR5 alongside the 4th generation Intel Xeon processor in January 2023. This process has been crucial for overcoming obstacles in the evolution of 10 nm process technology and continues with the recent development of 1c DDR5, which reaches operational speeds of 8 gigabits per second and improves energy efficiency by 9% compared to its predecessor, 1b DDR5.

The Future of Validation in DRAM Products

With the success of its 1c DDR5, SK hynix is laying the groundwork for its future product lines, including HBM5, LPDDR6, and GDDR7. To further enhance validation efficiency, the company plans to strengthen collaboration with SoC companies and optimize sample production. Furthermore, it is expected to implement a system that minimizes the resources needed for the validation process, proactively addressing market demands.

In the words of Yoosung Lee, Technical Lead for DRAM Product Planning, “The goal is to build a validation process that achieves maximum results with minimal resources, enhancing collaboration with SoC companies and optimizing our validation strategies.”

With innovative validation ensuring the quality and compatibility of its products, SK hynix is advancing towards the future of high-speed memory, ready to meet the increasing demands of AI and big data in a competitive global market.

via: SK Hynix