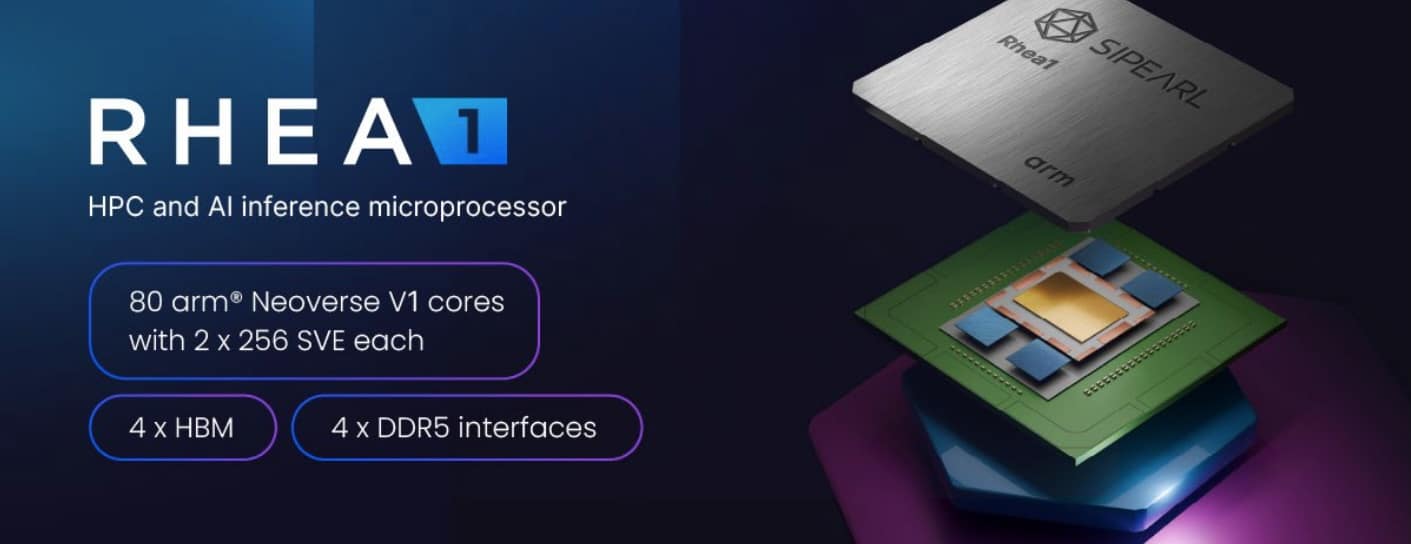

At the Hamburg ISC event, French company SiPearl unveiled the technical specifications of its first microprocessor, Rhea1, specifically designed for high-performance computing (HPC) workloads and AI inference. This marks a key step in Europe’s effort to regain technological sovereignty in high-performance hardware.

Constructed on the Arm® Neoverse V1 platform, Rhea1 will feature 80 high-performance cores, each equipped with two 256-bit Scalable Vector Extension (SVE) units, making it particularly suitable for resource-intensive vector operations, such as scientific simulations or AI applications.

The processor also boasts an advanced memory architecture with four embedded High Bandwidth Memory (HBM) stacks, providing high capacity and bandwidth, ideal for memory-bound tasks like big data analysis, AI, or advanced scientific computing. Complementing this setup are four DDR5 interfaces, compatible with configurations of 2 DIMMs per channel (2DPC).

Rhea1 will offer 104 PCIe Gen5 lanes, distributed across six x16 and two x4 connections, ensuring extensive connectivity with GPUs, accelerators, or high-performance storage systems.

Thanks to Arm’s CMN-700 Coherent Mesh Network on Chip (NoC), Rhea1 will efficiently manage internal communications between cores, memory interfaces, and peripherals. It will support both flat and quadrant modes, providing flexibility for various HPC topologies and configurations.

The processor will be compatible with traditional programming languages like C, C++, Go, and Rust, as well as next-generation AI frameworks such as TensorFlow and PyTorch, making it a versatile option for data scientists and supercomputing engineers alike.

According to Philippe Notton, founder and CEO of SiPearl, “Rhea1 combines the performance of Arm Neoverse V1 cores with unparalleled energy efficiency, thanks to our patented innovations in memory and power management. It’s designed to be a cost-effective and flexible alternative to current AI inference solutions.”

The launch of Rhea1 aligns with the goals set by the European Processor Initiative (EPI) and the EuroHPC Joint Undertaking, aiming to deploy a world-class supercomputing infrastructure in Europe. Its applications will target strategic sectors such as medicine, defense, security, energy transition, climate change, and increasingly, generative AI models.

With over 190 employees across France, Germany, Italy, and Spain, SiPearl leads the development of purpose-built processors focused on efficiency and European technological independence.

Furthermore, Rhea1’s use of an Arm-based architecture, instead of proprietary architectures like x86, opens new possibilities for customization, sustainability, and scalability in future data centers.

The first sampling of Rhea1 is scheduled for 2025, with production carried out in collaboration with TSMC in Taiwan, strengthening ties between the European and Asian semiconductor industries.

Technical features of Rhea1:

- 80 Arm® Neoverse V1 cores

- 2 SVE units of 256 bits per core

- 4 integrated HBM memory stacks

- 4 DDR5 interfaces (2DPC)

- 104 PCIe Gen5 lanes (6 x16 + 2 x4)

- Arm CMN-700 NoC network

- Support for Flat and Quadrant modes

- Compatibility with C, C++, Go, Rust, TensorFlow, and PyTorch

Conclusion

Rhea1 represents Europe’s committed bid to compete in supercomputing and AI with a proprietary, efficient, and scalable architecture. SiPearl aims not only for technological independence but also to offer a viable and strategic alternative to the dominance of major U.S. and Asian manufacturers.

Will Rhea1 become the new European standard for HPC centers and AI inference clusters? We’ll find out in 2025.