For years, the semiconductor battle was almost always viewed through the lens of node, lithography, or the chip designer. But the AI craze has shifted part of that conversation into a less glamorous but equally critical area for the general public: advanced packaging. Here is where TSMC has turned CoWoS into a central component of the AI accelerator ecosystem, while Intel is trying to make headway with EMIB and its evolution EMIB-T as an increasingly serious option within its foundry business.

The official overview paints a pretty clear picture. TSMC defines CoWoS as a technology designed for high-performance computing, integrating logic chiplets and HBM memory, directly linking it to AI applications and supercomputing. Conversely, Intel presents EMIB as a 2.5D system for connecting multiple complex chips within a single package, also supporting logic configurations with HBM. It emphasizes that this technology has been in production since 2017. EMIB-T adds through-silicon vias (TSVs) to strengthen integration and facilitate the fitting of designs from other packaging schemes.

This contrast helps explain why the debate is no longer only about who makes better chips but also about who can best, fastest, and with a more resilient supply chain integrate them. The NIST, through the U.S. CHIPS National Advanced Packaging Manufacturing Program, sums it up bluntly: semiconductor investments will only succeed with investments in advanced packaging. This is not a minor detail. It’s an official acknowledgment that the bottleneck isn’t just the wafer fab but also how these increasingly complex chips are assembled, interconnected, powered, and validated.

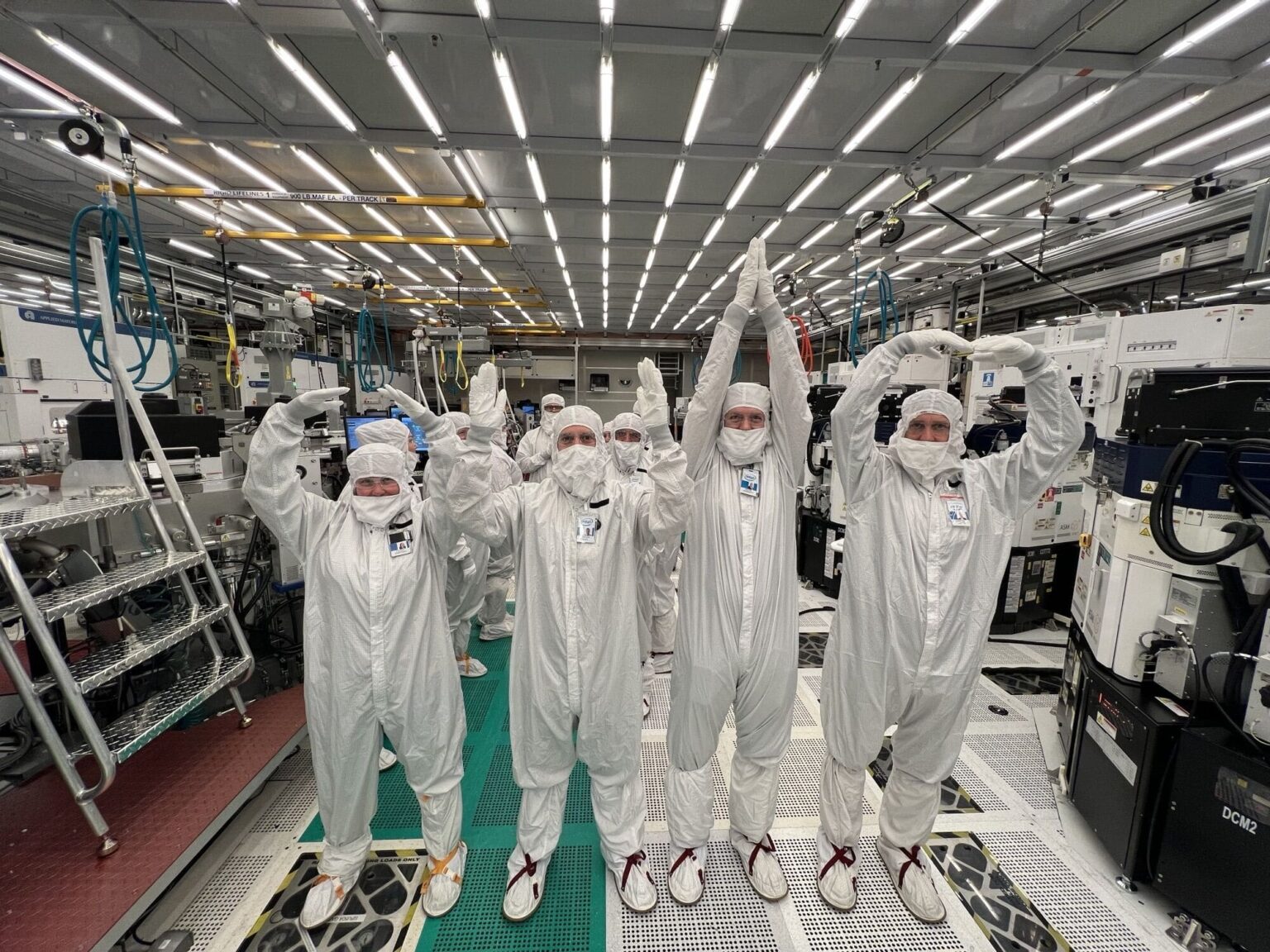

Intel is aiming to leverage exactly this window. The company has been working to convince the market that its offer is not only a technical answer but also an industrial and geographic one. In January 2024, it opened Fab 9 in Rio Rancho, New Mexico, within a $3.5 billion investment, presenting it as its first operational site for mass production of advanced 3D packaging. At that time, Intel described the facility as the only factory in the U.S. producing at scale its cutting-edge advanced packaging solutions. From an industrial storytelling perspective, it was a way to say that the company not only has the technology but also genuine domestic capacity.

The bottleneck is no longer just in chip manufacturing

Market pressure helps explain why this issue has gained such importance. Generative AI has skyrocketed demand for high-performance chips, but that demand depends not only on more advanced wafers. It also requires ultra-dense interconnections, HBM memories, thermal dissipation, signal integrity, and controlled power consumption within increasingly complex packages. In this context, advanced packaging is no longer just the final manufacturing stage but a strategic part of the product.

TSMC still has the edge here. Its 3DFabric platform combines technologies like CoWoS, SoIC, and InFO, and the company has placed CoWoS at the center of its proposals for AI and HPC. Moreover, far from staying idle, TSMC announced in March 2025 that it would expand U.S. investments to $165 billion, including two advanced packaging plants in Arizona. This move is significant because it deflates an overly simplistic market narrative: Intel is not competing alone as an “American response,” since TSMC is also bringing part of its capacity onto U.S. soil.

However, Intel does have a notable advantage. While TSMC is expanding, Intel already has an established industrial base for advanced packaging in the U.S., which it uses as a selling point to attract clients seeking greater supply chain resilience. In semiconductors, reducing transport, simplifying assembly, and avoiding unnecessary dependencies are no longer just logistical issues—they impact cost, timelines, and geopolitical risks. This is especially relevant for fabless companies that want to manufacture in the U.S. or keep a significant part of their supply chain closer.

Intel plays the card of local capacity and flexibility

The technical proposal behind EMIB also makes sense within this strategy. Intel describes it as an efficient and cost-effective way to connect multiple complex dies via a silicon bridge embedded in the package substrate, avoiding the need for a larger interposer like in other 2.5D approaches. On paper, this offers advantages in cost, design flexibility, and simplified manufacturing for certain product types. Additionally, EMIB-T incorporates TSVs into the bridge—a development aimed at reinforcing power delivery and interconnection for next-generation AI designs.

This nuance is important because not all products require exactly the same features. CoWoS has excelled mainly in configurations where integrating large amounts of HBM and maximizing bandwidth for demanding accelerators are priorities. EMIB, on the other hand, can be particularly attractive in projects emphasizing physical scalability, cost efficiency, and modularity. In practice, it’s unlikely that one technology will entirely replace the other; instead, they may coexist, each gaining ground where it best fits.

What seems clear is that Intel aims to make EMIB regarded not just as a promising but secondary technology but as a key component in the new AI landscape. Its recent messages about foundry, packaging, and systems for AI are aligned with this: positioning EMIB-T not as a technical curiosity but as an industrial tool ready for large, heterogeneous designs with substantial power needs.

That said, it’s wise to clearly distinguish the measurable facts from market noise. Official sources confirm that Intel has a mature advanced packaging offering, that EMIB has been in production for years, that EMIB-T extends this portfolio, and that the company has industrial capacity in the U.S. They also confirm that TSMC continues to regard CoWoS as a benchmark for AI and is expanding its advanced packaging presence in Arizona. However, client lists, multimillion-dollar contracts, or third-party product commitments reported unofficially should not be assumed closed without concrete announcements. In such a sensitive sector, the difference between expectations and firm orders remains vast.

At the core, this movement reflects a fundamental shift: the AI chip business is no longer solely decided by transistor manufacturing plants. It also depends heavily on packaging, industrial proximity, the ability to integrate memory and logic without cost explosions, and offering clients a less exposed supply chain. TSMC currently holds a clear advantage, but Intel has identified EMIB as a credible way to join the conversation. In a market where advanced packaging has become a strategic bottleneck, that’s no small detail.

Frequently Asked Questions

What’s the difference between Intel EMIB and TSMC CoWoS in AI chips?

EMIB uses an embedded silicon bridge within the substrate to connect multiple dies in a package, while CoWoS relies on advanced interposers and integration technologies heavily oriented toward HPC and AI with HBM. Broadly speaking, CoWoS has become the reference for large AI accelerators, whereas EMIB aims to gain ground with a more flexible approach and strong industrial presence in the U.S.

Why is advanced packaging so critical for AI?

Because modern AI chips no longer depend solely on the fabrication node. They need to integrate multiple chiplets, HBM memory, stable power delivery, thermal management, and high-density interconnects. NIST emphasizes that a competitive semiconductor industry will require a solid foundation in advanced packaging.

Does Intel have advanced packaging capacity in the U.S.?

Yes. Intel opened Fab 9 in New Mexico in 2024 and integrated it with Fab 11X as its first large-scale operation for 3D advanced packaging. It positions this as a key element to reinforce its supply chain and domestic industrial footprint.

Will TSMC also implement advanced packaging in Arizona?

Yes. TSMC announced in 2025 that it will increase U.S. investment to $165 billion, including two advanced packaging facilities in Arizona. This underscores that competition for advanced backend capacity is also shifting into the U.S. market.