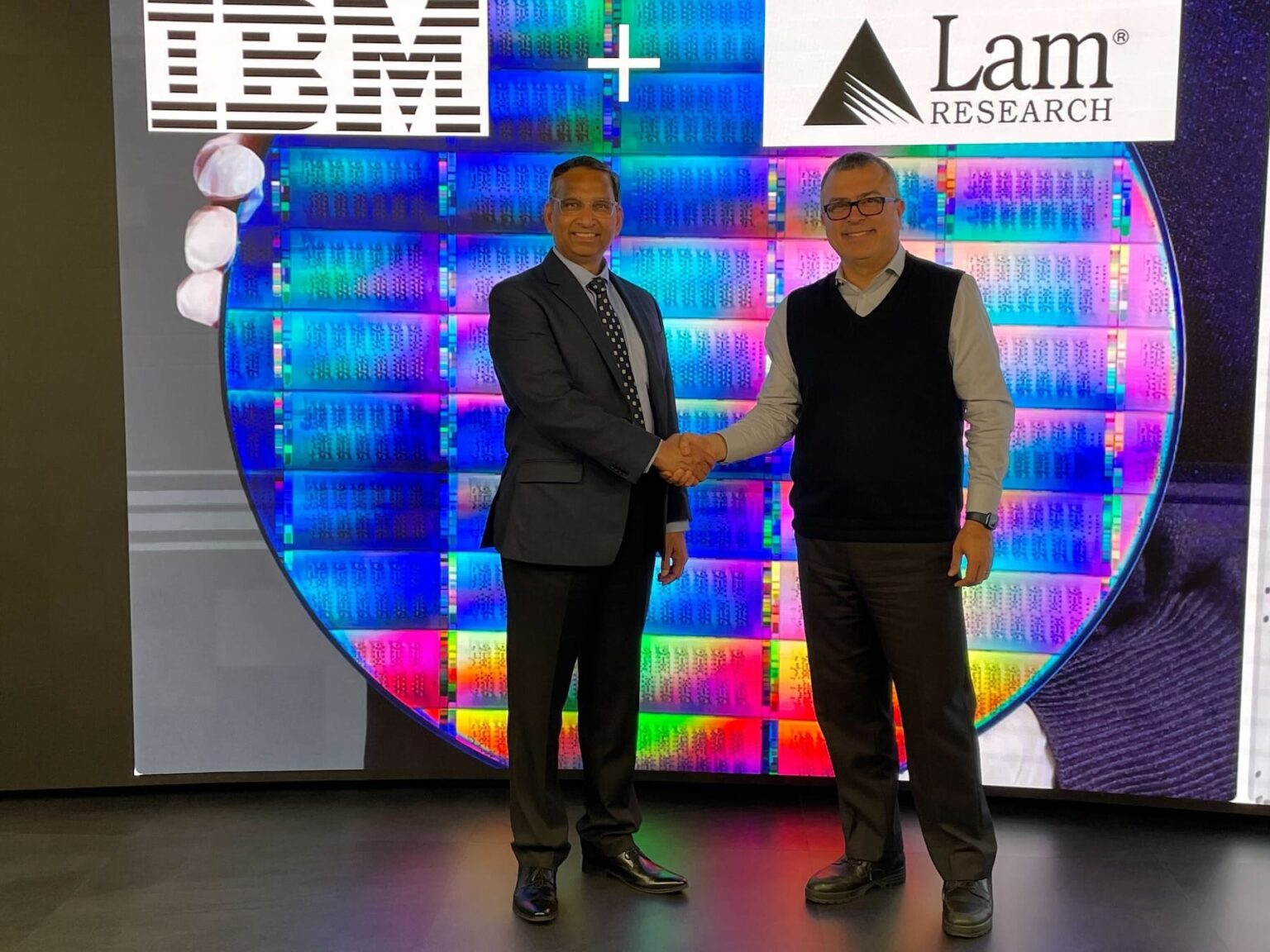

IBM and Lam Research have announced a new five-year collaboration aimed directly at the future of the semiconductor industry: developing materials, manufacturing processes, and High NA EUV lithography techniques to continue shrinking logic chips below the 1-nanometer node. The announcement does not imply that sub-1 nm chips will reach the market in the near term but confirms that both companies want to position themselves in one of the most complex and decisive technological races of the next decade.

The partnership also builds on a longstanding relationship within the industry. IBM and Lam note that they have been collaborating for over a decade on advanced manufacturing technologies, which has already contributed to milestones such as 7 nm processes, nanosheet architectures, and EUV lithography advances. IBM emphasizes that in 2021, it introduced its first 2 nm chip—a technological demonstration that reinforced its role as a leading player in semiconductor research, though it does not produce chips at volume like a foundry such as TSMC or Samsung.

A research initiative, not an immediate product

The most important aspect of the announcement is understanding what was actually signed. This is not a new commercial production line or a node ready for volume manufacturing but rather an R&D agreement focused on building and validating complete process flows for future generations of advanced logic. The work will follow IBM’s logical scaling roadmap and will focus on new materials, advanced etching and deposition capabilities, and High NA EUV processes capable of transferring increasingly smaller patterns onto actual device layers with viable yields.

That nuance is crucial because the leap below 1 nm doesn’t depend on a single isolated improvement. The industry has reached a point where further miniaturization isn’t just about making everything smaller but rather about combining new materials, 3D architectures, finer patterning techniques, and extreme control over defects, variability, and power consumption. Lam states in its announcement that this is directly linked to a new era of 3D scaling where materials, processes, and lithography must function as a much more integrated high-density system than before.

The role of High NA EUV lithography

One of the most significant elements of the collaboration is the explicit focus on High NA EUV lithography. ASML, a key provider of this technology, explains that its new-generation EXE systems increase numerical aperture from 0.33 to 0.55, improving resolution and enabling the printing of much smaller features with less complex patterning techniques. For example, the EXE:5000 system claims it can achieve resolutions of 8 nm and fabricate features 1.7 times smaller than those possible with previous EUV generations, significantly increasing transistor density.

For IBM and Lam, however, this lithography improvement alone is not enough. Therefore, the agreement also includes developing processes targeted at future interconnect architectures such as nanosheets, nanostacks, and backside power delivery. The latter is especially important because backside power delivery is becoming one of the most promising techniques for scaling performance and efficiency without heavily burdening front-end interconnect design. In other words, the challenge now extends beyond etching smaller structures to ensuring that entire transistors and their electric networks remain manufacturable and functional at scale.

Albany NanoTech and the tools involved

The research will leverage IBM’s capabilities at the Albany NanoTech complex, managed within the NY CREATES ecosystem in New York State. This environment has long served as a hub for collaboration among major industry players. IBM and Lam will combine these research capabilities with Lam’s tools and platforms like Aether for dry resist, Kiyo and Akara for etching, Striker and ALTUS Halo for deposition, along with various advanced packaging technologies. NY CREATES has also publicly emphasized the importance of this collaboration for its campus, reinforcing Albany’s role as one of the leading centers for applied semiconductor research in the United States.

The inclusion of Aether in the agreement is not a minor detail. Lam has long argued that its dry resist technology can overcome limitations that become critical at advanced nodes, such as defectivity, pattern collapse, and maintaining precision as pitches shrink. In 2025, the company announced that Aether had been adopted as a reference production tool by a major memory manufacturer for advanced DRAM processes and has emphasized in subsequent publications that this approach could be particularly useful at or below 2 nm logic.

Implications for the industry

This announcement has a clear strategic message. As demand for chips for AI, cloud, and high-performance computing continues to grow, the pressure to keep pace with technological scaling intensifies. IBM is not currently competing in volume manufacturing of advanced logic chips but maintains influence as a research laboratory whose innovations can eventually impact foundries and industry partners. Lam, meanwhile, needs the industry to progress toward more complex nodes to support increasing demands for more sophisticated patterning, etching, and deposition equipment. This partnership underscores the idea that the next major frontier in semiconductors won’t be solved by a single machine or material but by fully integrated process chains driven by research and development.

It also carries an implicit message to the broader ecosystem. High NA EUV is no longer a distant promise but an emerging reality. ASML claims that this new generation of systems is ready to usher in a new phase of advanced manufacturing, with some industry players already installing their first commercial tools. However, transitioning from having the equipment to establishing stable, cost-effective, high-yield processes remains a significant challenge. That’s precisely where the IBM-Lam partnership fits in: in the less visible but critical phase of transforming laboratory promise into viable industrial technology.

In this context, the announcement should not be viewed as the imminent arrival of “sub-1 nm chips,” but rather as a serious effort to lay the groundwork. The race to scale logic further is increasingly costly, collaborative, and requires integrating lithography, chemistry, materials, 3D integration, and new electrical architectures. IBM and Lam aim to be involved from the beginning. Although it will take years before concrete commercial products emerge, the direction is clear: the next leap in semiconductors is happening now in labs, process tools, and pilot lines like those at Albany.

FAQs

What exactly have IBM and Lam Research announced?

They signed a five-year collaboration agreement to research materials, manufacturing processes, and High NA EUV lithography techniques to continue scaling logic chips below 1 nm. This is not a commercial launch but an R&D program.

What is High NA EUV and why is it important?

High NA EUV is the next generation of extreme ultraviolet lithography with a numerical aperture of 0.55. According to ASML, this technology offers better resolution than previous EUV systems and enables printing smaller features with less complex patterning, which is crucial for future logic nodes.

When will sub-1 nm chips reach the market?

No specific date has been announced. The agreement focuses on research and process validation, so any industrial deployment is still several years away.

What role does Albany NanoTech play in this collaboration?

The work will rely on IBM’s research capabilities at the Albany NanoTech Complex within the NY CREATES ecosystem, where both companies will develop and validate process flows for future generations of logic devices.

via: LAM Research