The semiconductor industry continues to advance, but each new leap requires more time, more money, and architectural changes. The old idea that transistors simply got smaller with each generation no longer fully explains what is happening. In the angstrom era, improvements will come from a much more complex mix: new transistors, vertical stacking, alternative materials, finer interconnections, backside wafer power delivery, and advanced packaging.

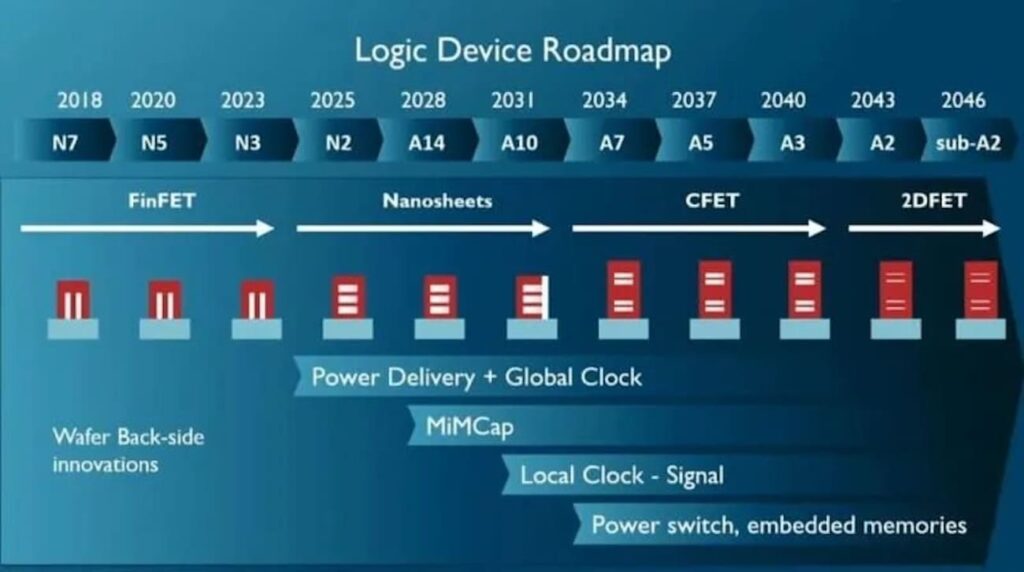

The roadmap attributed to imec, the Belgian nanoelectronics research center, projects the first node below 1 nm around 2034. This point would correspond to the A7 node, equivalent to 0.7 nm or 7 angstroms, marking the entrance of CFETs—an architecture that stacks n-channel and p-channel transistors vertically to continue increasing logical density. Later, around 2043, 2D FETs would appear at the A2 node, with two-dimensional materials as a possible way to push miniaturization beyond current limits.

It’s important to clarify that these figures should not be read as promises of exact commercial production. In semiconductors, node names no longer describe literal physical dimensions but serve as technological and commercial labels. The roadmap indicates research and development phases, not necessarily that a specific manufacturer will sell 0.7 nm chips in 2034 or 0.2 nm in 2043. Still, the timeline helps understand where the industry is heading.

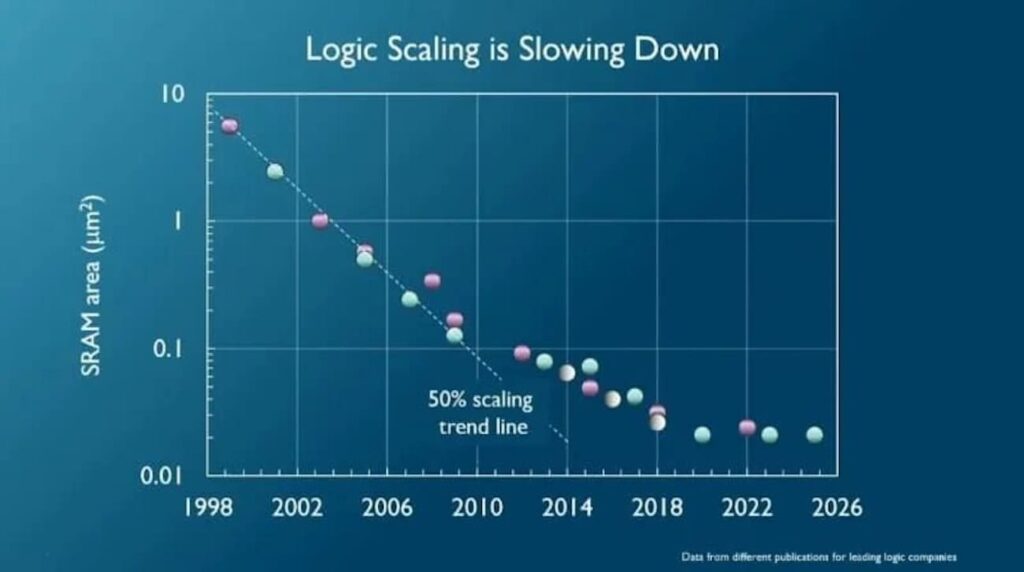

Moore’s Law is not dead, but it no longer marches the same

For decades, the industry relied on aggressively shrinking transistor sizes. Between the late 1990s and the early 2000s, logical density improved at a pace that made doubling performance or reducing costs viable with each generation. This momentum has slowed. The reduction in SRAM cell area—which has been a key indicator of node scalability—has been losing speed for years, and in recent nodes, progress has become much less spectacular.

The challenge isn’t only physical. Manufacturing at advanced nodes requires EUV lithography, more complex processes, additional masks, more process steps, and significant investment in factories. That’s why major chip manufacturers and designers are increasingly turning to chiplets, 2.5D, 3D IC, interposers, and advanced packaging. Instead of consolidating everything onto a single, massive die, they combine specialized blocks manufactured at different nodes and interconnected with increasingly sophisticated techniques.

Artificial intelligence and high-performance computing have accelerated this trend. Modern accelerators don’t rely solely on smaller transistors; they also require high-bandwidth memory (HBM) close to the processor, very high bandwidth interconnects, efficient power delivery, and effective thermal management. The race isn’t just about node size but encompasses entire system architectures.

Nonetheless, logic will continue to scale. The roadmap envisions a clear transition from FinFET to nanosheet transistors, then to CFETs, and eventually to transistors based on 2D materials. Each leap aims to solve the same dilemma: how to increase density and performance when traditional horizontal scaling is no longer sufficient.

| Approximate Period | Node | Proposed Architecture | Main Idea |

|---|---|---|---|

| 2018-2023 | N7, N5, N3 | FinFET | Last major FinFET stage on advanced nodes |

| 2025 | N2 | Nanosheet / GAA | Introduction of gate-all-around transistors |

| 2028 | A14 | Improved Nanosheet | Higher density and architectural tweaks |

| 2031 | A10 | Advanced Nanosheet | Final stretch before sub-1 nm |

| 2034 | A7 | CFET | First node expected below 1 nm |

| 2037 | A5 | Improved CFET | More vertical scaling and optimization |

| 2040 | A3 | Advanced CFET | Extension of CFET architecture |

| 2043 | A2 | 2D FET | Introduction of 2D materials |

| 2046 | Sub-A2 | Advanced 2D FET | Continuity scenario beyond 0.2 nm |

CFET and 2D FET: stacking and material innovation

The immediate next step is already underway with nanosheet FETs, also known as GAA or gate-all-around. The idea is to wrap the transistor channel all around with the gate, improving electrical control compared to FinFETs. TSMC, Samsung, and Intel are developing their versions of this transition, each with different commercial names and schedules.

The subsequent major phase is CFET. In a CFET architecture, nMOS and pMOS transistors are stacked vertically rather than laid out side by side. This approach reduces cell area and boosts density without relying solely on narrowing device dimensions. Imec has indicated in technical publications that CFET is an attractive architecture for nodes beyond 1 nm and has explored various integration pathways, including monolithic and sequential stacking.

The next leap would involve 2D FETs. Here, we’re not just reorganizing silicon transistors but introducing two-dimensional materials in the conduction channels. These materials can maintain desirable electrical properties at extremely small scales. The challenge is translating this into industrial manufacturing with performance, uniformity, electrical contact, and reliability. While research shows promise, mass production still faces significant hurdles.

That’s why the 2043-2046 horizon should be approached with caution. It’s not a product launch date but a research vision outlining potential milestones if the industry overcomes challenges related to materials, processes, interconnections, power delivery, and thermal management.

The bottleneck also lies in connections

Shrinking transistors isn’t enough if interconnections between transistors become the limiting factor. BEOL (Back-End-Of-Line) layers, responsible for the metal interconnects, are among the most critical zones. As metal pitches decrease, resistance, congestion, and thermal issues increase. Copper, dominant for years, begins to face difficulties at very small scales due to barrier requirements and volume loss.

The roadmap suggests a gradual shift toward materials like rutenium and techniques such as semi-damascene or subtractive metallization, along with air gaps and self-aligned vias. In upcoming nodes near 2 nm, metal pitches could be as small as 24-26 nm; at A14, they might reduce to 20-22 nm; at A10, around 18-20 nm; and at A7, possibly 16-18 nm. For A5 and A3, targets fall within a 12-16 nm range, still in research phases.

| Approximate Year | Node | Minimum Metal Pitch | Highlighted BEOL Technologies |

|---|---|---|---|

| 2025 | N2 | 24-26 nm | Copper, dual/single damascene |

| 2028 | A14 | 20-22 nm | Current process improvements |

| 2031 | A10 | 18-20 nm | Transition to rutenium, air gaps, self-aligned vias |

| 2034 | A7 | 16-18 nm | Semi-damascene / subtractive metallization |

| 2037 | A5/A3 | 12-16 nm | Exploratory alternative materials |

This aspect often receives less public attention—more focused on terms like “2 nm” or “1.4 nm”—but it’s decisive. A chip’s performance doesn’t improve just because its transistors are denser. If power supply, signals, and heat dissipation aren’t equally optimized, real performance limits will be reached or consumption will spike.

Backside power delivery and heat management

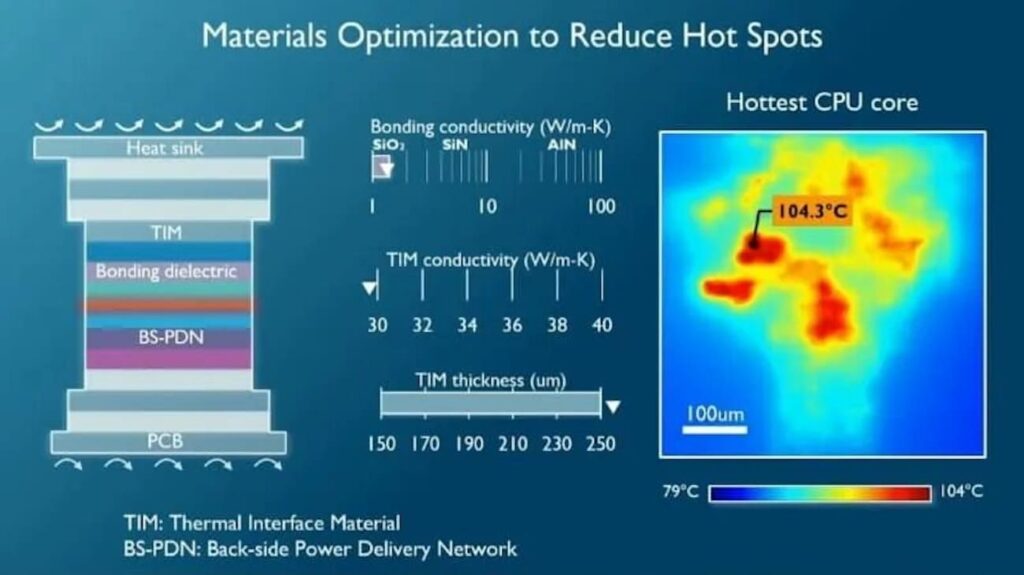

Another key factor is power delivery. Traditional networks bring signals and power through the front of the wafer, occupying space in many metal layers. Backside power delivery networks (BSPDN) separate some of this routing, freeing front-side space for signals. The potential advantage is clear: less congestion, better current delivery, and more headroom for scaling.

But it’s not without costs. Moving the power network alters thermal paths and can complicate heat dissipation. Imec’s technical analyses of backside power delivery highlight the need to carefully study design options and thermal trade-offs. In high-performance chips—where heat is already a serious constraint—any physical change has significant consequences.

The roadmap also mentions integrating voltage regulators on the package, interposer, or even the wafer’s backside. For AI systems and high-performance computing, providing stable power to multiple chiplets, HBM stacks, and accelerators requires a more precise electrical architecture. Power no longer remains external to the chip; it becomes part of the sophisticated system design.

The core message of the roadmap is that the future of semiconductors depends not on a single miracle technology but on orchestrating new transistors, more efficient wiring, power delivery, materials, 3D packaging, near-memory storage, and thermal management. Miniaturization continues, but it no longer progresses in isolation.

If the projections hold, reaching sub-1 nm chips will not be a simple node change. It will be the culmination of nearly a decade of technological development—from current nanosheets to CFETs and, eventually, to 2D materials. Simultaneously, the industry will need to justify each step economically. With ever-costlier fabs and increasing importance of advanced packaging, not every product will require the most cutting-edge node.

The major AI accelerators, high-performance CPUs, and data center chips will continue pushing the frontier. The rest of the market will likely combine mature nodes, chiplets, and packaging techniques to balance cost and performance. Moore’s law is alive but more costly, more vertical, and far more complex to summarize with a single nanometer number.

Frequently Asked Questions

When will chips below 1 nm arrive?

Imec’s roadmap places the first sub-1 nm node around 2034, with the A7 or 0.7 nm node based on CFET. This is not a guaranteed commercial production date.

What is a CFET?

A CFET is a complementary transistor that stacks nMOS and pMOS devices vertically to enhance logical density beyond what conventional nanosheets can achieve.

What are 2D FETs?

They are transistors that use two-dimensional materials in the conduction channel. They are being studied as a route to extend logical scalability toward nodes of 0.2 nm and smaller.

Why isn’t reducing transistor size enough anymore?

Because current limits also come from interconnects, power delivery, heat, memory, and manufacturing costs. Modern performance increasingly depends on the overall system design.

Source: 36kr