Artificial intelligence has just taken a new step in one of the most complex fields of engineering: semiconductor design. The startup Verkor.io claims that their Design Conductor system was able to autonomously create a complete RISC-V CPU core, called VerCore, based only on a 219-word requirements document and in 12 hours.

The claim is striking, but it’s important to read it carefully. It’s not that a language model physically manufactured a processor or designed a CPU comparable to modern chips from Intel, AMD, Apple, or Arm. What Verkor.io asserts is that their AI agent has traversed the entire digital design flow, from the initial specification to a GDSII file, the layout format used in the final stages before manufacturing an integrated circuit.

A simple processor, but designed from end to end

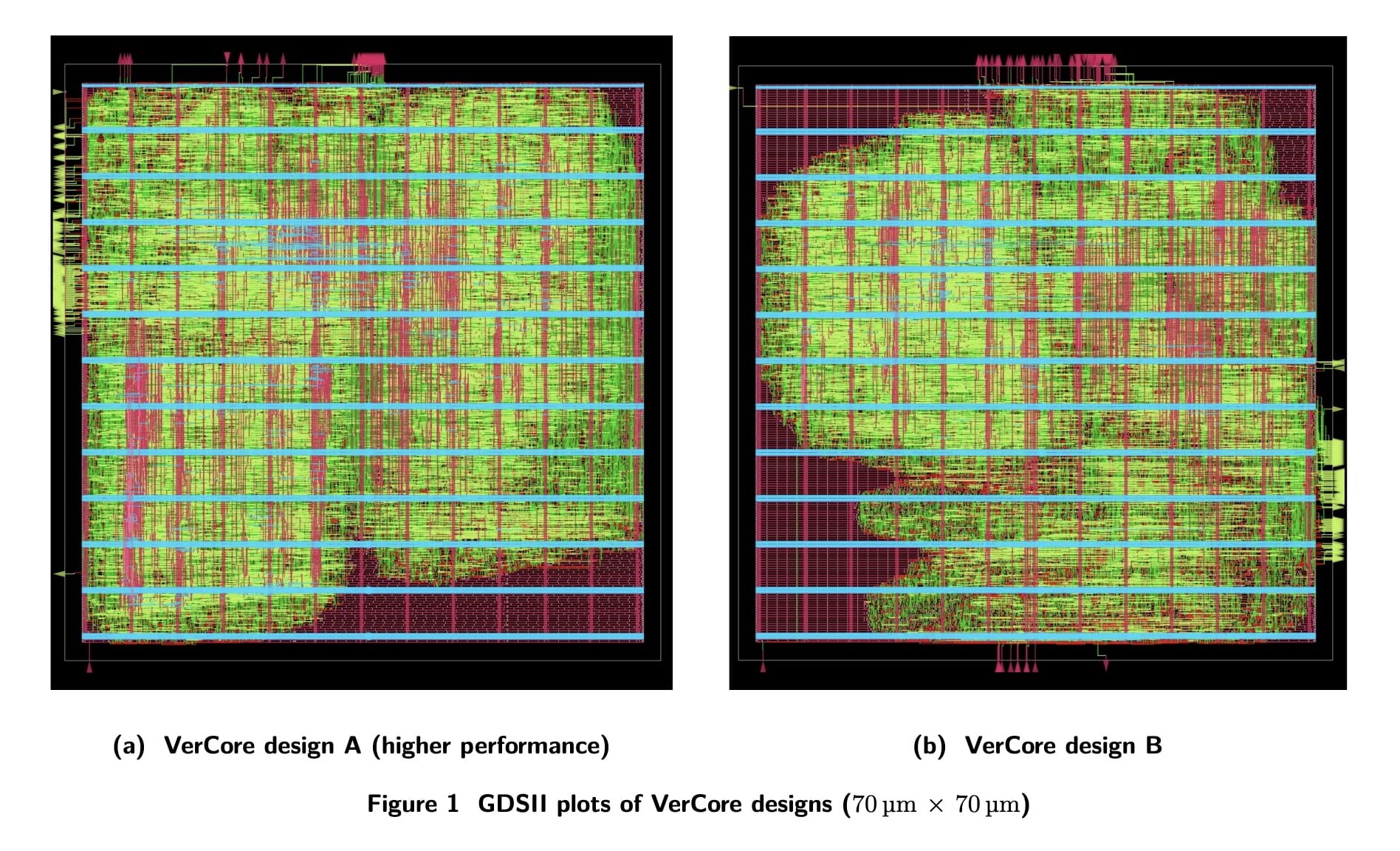

VerCore is presented as a RISC-V core compatible with RV32I and ZMMUL, with a straightforward five-stage architecture, in-order execution, and a single instruction per cycle. According to the technical report published by Verkor.io, the design achieved a frequency of 1.48 GHz using ASAP7, an academic predictive process design kit for 7nm technology, and scored 3,261 on CoreMark, a common benchmark for measuring the performance of microcontrollers and embedded CPUs.

The report itself compares this result to that of a 2011 Intel Celeron SU2300, a modest processor even by standards over a decade old. This comparison provides context: VerCore is not a competitor to current high-end chips nor does it aim to be. Its interest lies in the process, not just the final power of the chip.

Design Conductor is not exactly an isolated AI model but rather an orchestration tool guiding advanced models to perform design, review, debugging, and optimization tasks. In this case, the system received a brief specification requesting a RISC-V CPU with instruction cache interface, data cache interface, five-stage pipelined design, support for RV32I and ZMMUL, no compressed instructions, and a target CPI of 1.5 or lower.

From there, the agent generated microarchitecture proposals, implemented modules in Verilog, created testbenches, compared processor behavior with Spike — the reference RISC-V simulator — debugged functional errors, and adjusted the physical design using electronic design automation tools.

The importance of GDSII and a key nuance: not fabricated yet

Reaching GDSII is significant because this file represents the physical layout of the chip—an advanced description prepared for final manufacturing stages. Traditionally, semiconductor development involves architects, RTL engineers, verification specialists, timing experts, backend teams, and a very complex flow of EDA tools.

The Verkor.io document notes that developing a cutting-edge chip can cost over 400 million dollars and take 18 to 36 months with teams of hundreds of engineers. In this context, having an agent produce a functional, simulatable design in 12 hours is noteworthy—even if the example is a relatively simple CPU.

The main caveat is that VerCore has not yet been manufactured. Its design has been validated via simulation and implemented on ASAP7, an academic PDK developed by Arizona State University in collaboration with ARM Research. This means it’s not a commercial chip ready for market but a technical demonstration of an automated design flow.

Additionally, the verification process for a real chip intended for mass production is much more demanding than passing functional tests and benchmarks in simulation. In semiconductors, discovering an error after tape-out can be extremely costly. Therefore, verification often accounts for a large part of the total development effort.

What AI contributes to chip design

The most intriguing aspect of Verkor.io’s work is how the agent seemingly followed a methodology similar to a human team: designing, testing, finding errors, correcting them, and re-measuring. The report describes how Design Conductor analyzed VCD traces, converted simulation data into CSV files, identified write failures in registers, and fixed pipeline vacuoting logic errors after jumps.

The system also explored microarchitecture variants. According to the document, it tested designs with one- and two-cycle penalty branch prediction, incorporated early forwarding, and arrived at a solution using a four-stage Booth-Wallace multiplier. Not all of these decisions were specified initially, suggesting a degree of technical exploration within a measurable goal.

Nevertheless, the report admits significant limitations. Models can reason imperfectly about Verilog, sometimes confuse hardware behavior with that of a sequential program, and make suboptimal decisions before correcting them with real timing reports. In other words: AI can accelerate the process but still requires expert guidance to avoid wrong paths.

RISC-V as a natural testing ground

The choice of RISC-V is no coincidence. It is an open and modular instruction set architecture maintained by RISC-V International, which has become a particularly attractive field for research, education, microcontrollers, custom designs, and new specialized chips.

Its openness facilitates experiments by universities, startups, and companies with fewer licensing barriers compared to proprietary architectures. Coupled with open tools like OpenROAD and academic kits such as ASAP7, RISC-V offers an ideal platform to test how far automation can go in hardware design.

The VerCore precedent isn’t novel either. Recent years have seen experiments applying AI to digital synthesis, Verilog generation, and simple circuit design. What’s new, according to Verkor.io, is connecting these capabilities into a complete flow—from specification to the GDSII layout of a working CPU.

The next step is to see if other engineers can reproduce the results. Verkor.io has announced plans to publish relevant design files, allowing third parties to review the RTL, scripts, and build flow. They also plan to showcase a VerCore FPGA implementation at the Design Automation Conference in Long Beach, scheduled for July.

So, this news shouldn’t be seen as announcing a revolutionary CPU but rather as a signal of where semiconductor engineering might be headed. If these systems mature, they could reduce exploration times, enable more design variants, and help small teams tackle projects that today require much larger resources. Still, the leap from an academic demo to a reliable commercial chip remains enormous.

Frequently Asked Questions

What is VerCore?

VerCore is a RISC-V CPU core designed by Verkor.io’s agentic AI Design Conductor. It’s a simple 32-bit processor with a five-stage architecture, in-order execution, and support for RV32I and ZMMUL.

Has VerCore been fabricated as a physical chip?

No. Based on available information, VerCore has been validated in simulation and output as a GDSII layout, but it has not yet been physically fabricated as a commercial or silicon prototype chip.

What does it mean that an AI reached GDSII?

It means the system generated a physical layout of the circuit—a advanced stage of chip design. However, reaching GDSII alone doesn’t guarantee the chip is ready for mass production, as further validation and industrial processes are needed.

Can AI replace chip engineers?

Not yet. This case shows that AI can automate important parts of the design and speed up exploration, but the report itself emphasizes that architects and expert engineers are still essential to guide, review, and validate complex designs.