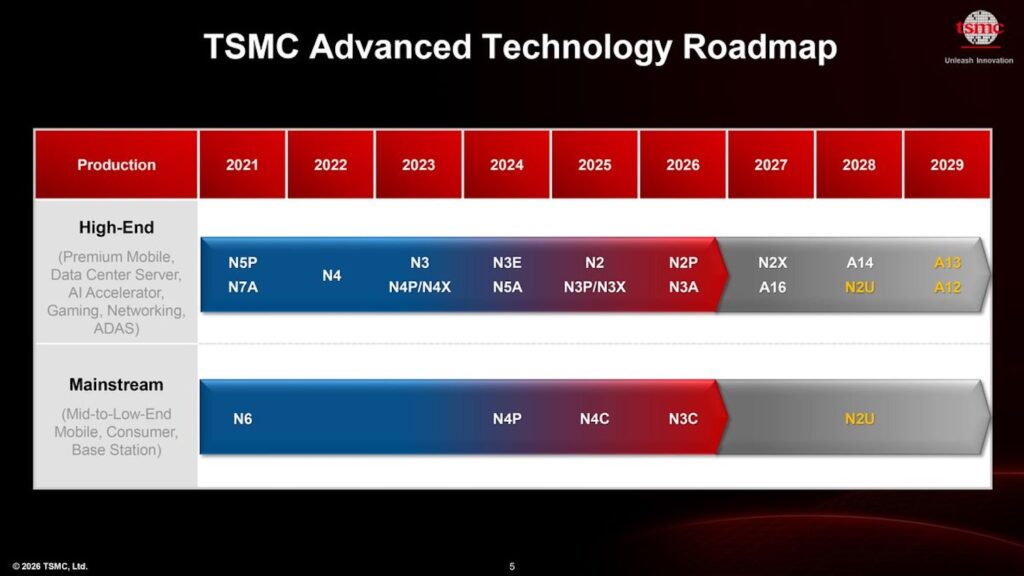

TSMC has used its Technology Symposium 2026 to unveil a roadmap that goes well beyond a simple incremental update. The Taiwanese company has set the dates and shaped the form for the next phase of its offensive in advanced logic, automotive, and AI packaging, with a sequence that is no longer limited to familiar names like N2, A16, and A14, but adds new components such as N2U, A13, A12, N2A, and an aggressive expansion of CoWoS, SoW-X, and SoIC. The message is clear: TSMC wants to continue leading not only in process nodes but also in memory integration, 3D stacking, and system density.

The most noteworthy part of the announcement is not just that TSMC keeps advancing—something that was already expected—but how they have organized their schedule through 2029. The company has better separated its “standard” evolution branch from the one focused on backside power delivery, while accelerating in packaging to respond to the real pressures of the AI market. Overall, the new roadmap reinforces the feeling that TSMC does not want to merely stay ahead of Intel and Samsung, but to force both to compete on multiple fronts simultaneously: process, power, memory, and integration.

N2U, A13, and A12: a more diversified roadmap

The first major innovation is N2U, a new extension of the 2 nm platform. According to TSMC, this node employs joint design and technology optimization to deliver between 3% to 4% higher speed or 8% to 10% lower power consumption compared to N2P, along with a logical density improvement of 1.02x to 1.03x. The company positions it as a balanced option for AI, HPC, and mobile applications, supported by the maturity and manufacturing performance of the 2 nm platform, with production expected in 2028.

Alongside this evolution, TSMC has announced A13, described as a direct shrink of A14. On paper, A13 will offer a 6% area reduction compared to A14, will maintain full design rule compatibility, and will incorporate energy efficiency and performance improvements through joint optimization. Production is scheduled for 2029, a year after A14. That design compatibility is not a minor detail: it facilitates customer migration without forcing a drastic break from the previous generation.

The third element in this advanced branch is A12, which TSMC presents as an enhancement of the A14 platform designed for AI and HPC, thanks to Super Power Rail, their backside power delivery technology. The company frames it as an evolution aimed at solving one of current silicon’s major bottlenecks: delivering power when density and current demands keep rising. Production is also planned for 2029.

Table: TSMC’s new roadmap until 2029

| Technology | Main Focus | Expected Date |

|---|---|---|

| N2U | Enhanced 2 nm with better balance of performance, power, and density | 2028 |

| A13 | Shrink of A14 with 6% less area and compatible rules | 2029 |

| A12 | Platform with Super Power Rail for AI and HPC | 2029 |

| N2A | First automotive node with nanosheets | 2028 (AEC-Q100 qualified) |

| CoWoS 14 reticles | Up to ~10 large compute dies and 20 HBM stacks | 2028 |

| CoWoS >14 reticles | Further expansion of packaging. | 2029 |

| SoW-X | Wafer-scale system integration of over 40 reticles | 2029 |

| A14-to-A14 SoIC | 3D stacking with 1.8x higher die-to-die I/O density | 2029 |

Source: TSMC North America Technology Symposium 2026.

Automotive and Physical AI: TSMC also advances with N2A

TSMC did not limit the discussion to mobile or data centers. At the same event, they announced N2A, described as their first automotive process with nanosheet transistors. The company claims it will deliver between 15% and 20% more speed at the same power compared to N3A and will achieve AEC-Q100 qualification by 2028. Additionally, TSMC will incorporate “Auto-Use” design kits within the N2P PDK to enable customers to start automotive-oriented development earlier.

This move is especially relevant because advanced automotive, ADAS systems, and what is called physical AI are beginning to require top-tier nodes with stricter reliability guarantees. TSMC aims to stay ahead with a dedicated offering, not just a delayed adaptation of its consumer nodes.

CoWoS, SoW-X, and SoIC: where much of the AI battle is played

If the logical roadmap is impressive, the packaging one perhaps says even more about the industry’s current state. TSMC confirmed it already produces CoWoS with 5.5 reticles and that in 2028 it will bring this technology to 14 reticles. This allows the integration of approximately 10 large compute dies and 20 HBM stacks in one package. Afterward, a version with more than 14 reticles will arrive in 2029. These advances are a direct response to the industry’s need to pack more compute and memory into a single encapsulation for AI workloads.

In addition, SoW-X, TSMC’s wafer-level system integration technology, is also expected in 2029, targeting more than 40 reticles. On the 3D stacking front, TSMC announced A14-to-A14 SoIC, ready for production in 2029 with 1.8 times higher die-to-die I/O density than N2-on-N2 SoIC. This figure is not cosmetic: in AI, internal bandwidth and physical proximity between dies are becoming as critical as lithographic node size.

Intel and Samsung continue in the race, but the bar is rising

It would be an exaggeration to say TSMC has “erased” all hope for Intel and Samsung. Both still have ambitious plans. Intel Foundry maintains its roadmap with Intel 18A, already ready for customer projects, and Intel 14A, with PowerDirect as an evolution of its backside power delivery, along with extensions like 18A-P and 18A-PT. Meanwhile, Samsung reaffirmed in 2024 its plans to start production on 2 nm in 2025 and 1.4 nm in 2027.

However, what TSMC’s roadmap clearly does is raising the competitive bar. It’s no longer enough to have an advanced node or promise backside power. The market now demands large-scale packaging solutions for AI, clear automotive roadmaps, HBM integration, and continuity in design across generations. Within this broader business perspective, TSMC continues to emerge as the best-coordinated actor overall.

Frequently Asked Questions

What exactly has TSMC announced in its roadmap through 2029?

TSMC has outlined new stages such as N2U, A13, A12, and N2A, along with advancements in packaging including CoWoS with 14 reticles, expansion to over 14 reticles, SoW-X, and A14-to-A14 SoIC by 2029.

What does A13 bring compared to A14?

According to TSMC, A13 is a direct shrink of A14 with 6% less area, full design rule compatibility, and additional efficiency and performance improvements. Production is scheduled for 2029.

What is N2U and why is it important?

N2U is a new variant of the 2 nm platform promising 3-4% higher speed or 8-10% lower power compared to N2P, along with a slight density improvement. It is expected to launch in 2028.

Does TSMC’s roadmap exclude Intel and Samsung?

Not definitively. Both continue with their own advanced plans, but TSMC’s roadmap reinforces its leadership by combining process node advancements, backside power, automotive focus, and advanced packaging within a more integrated strategy.

via: Tom’s Hardware and TSMC