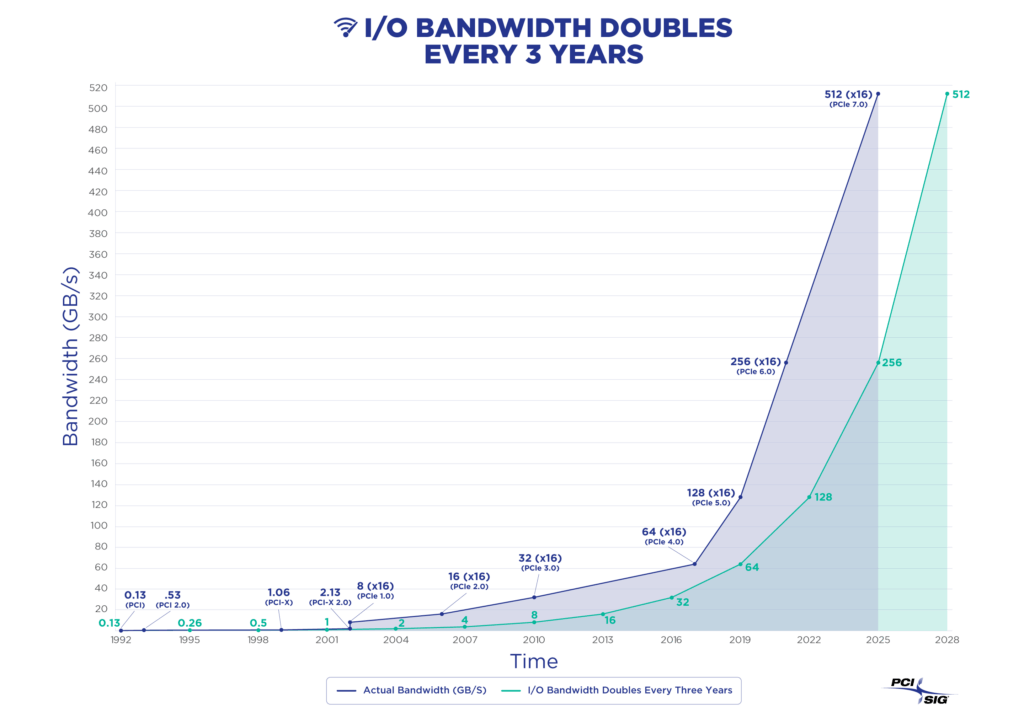

The PCI-SIG consortium has announced the release of the PCI Express 7.0 specification (version 0.9) for internal member review. This version, regarded as the final draft, represents a crucial step toward the official release of the standard, expected by the end of 2025. With this update, PCI-SIG reaffirms its historic commitment to doubling the bandwidth of the PCIe standard every three years.

The new PCIe 7.0 specification promises to achieve a raw transfer speed of 128 GT/s (gigatransfers per second), allowing for up to 512 GB/s of bidirectional bandwidth in x16 configurations. This advancement marks a technological leap intended to support sectors demanding intensive data processing, such as hyperscale data centers, high-performance computing (HPC), military/aerospace, and emerging applications like artificial intelligence, machine learning, cloud computing, and quantum computing.

Key Features of PCIe 7.0

The development of PCIe 7.0 has been guided by several key objectives:

- 128 GT/s speed and 512 GB/s bidirectional data transfer in x16 configuration.

- Use of PAM4 modulation (Pulse Amplitude Modulation with 4 levels), a signaling technique that allows more data to be sent per cycle.

- Improvements in channel parameters and reach to ensure stability at high speeds.

- Increased energy efficiency, in line with the growing demand for sustainability in IT infrastructures.

- Maintaining low latency and high reliability, fundamental characteristics of the PCIe standard.

- Full backward compatibility with all previous generations of PCIe, ensuring smooth market adoption.

Impact on the Tech Ecosystem

The announcement of the final draft of PCIe 7.0 has been met with enthusiasm from the industry, which sees this evolution as a response to the growing data transfer needs in strategic sectors. Since its inception in 1992, PCI-SIG has maintained the philosophy of “build it so they will come,” as noted by Nathan Brookwood, researcher at Insight 64, referring to the organization’s ongoing commitment to technological advancement.

The announcement of PCIe 7.0 once again places PCI-SIG at the forefront of innovation,” said Al Yanes, president of PCI-SIG. “As bandwidth demands continue to rise, our working groups are focused on improving channel reach and energy efficiency to meet the challenges of the future.”

What it Means for Future Applications

The PCIe 7.0 specification not only addresses current needs but also anticipates the future of technology. Applications such as 800 Gbps Ethernet, large-scale AI model training, next-generation cloud infrastructures, and quantum processing will greatly benefit from the increased bandwidth and low latency that PCIe 7.0 will offer.

Furthermore, traditional sectors such as ultra-fast data storage, next-generation graphics, and mission-critical servers will be able to leverage the speed and efficiency improvements that this new version will bring.

Path to Final Publication

The current state of the specification (version 0.9) indicates that no major functional changes are expected, as it is in the review phase to identify essential patents among members. The official release of version 1.0 is anticipated by the end of 2025, adhering to the planned schedule of triennial updates.

Members of PCI-SIG already have access to the documentation through the Review Zone portal or via the Causeway platform. Organizations interested in contributing to the development or benefiting early from the new specification can join the consortium through its official website.